引用:

原帖由 XT 於 2017-6-2 20:39 發表

Epyc 個走線 design 同 Ryzen 9 唔同...

原帖由 Sandbo 於 2017-6-2 22:56 發表

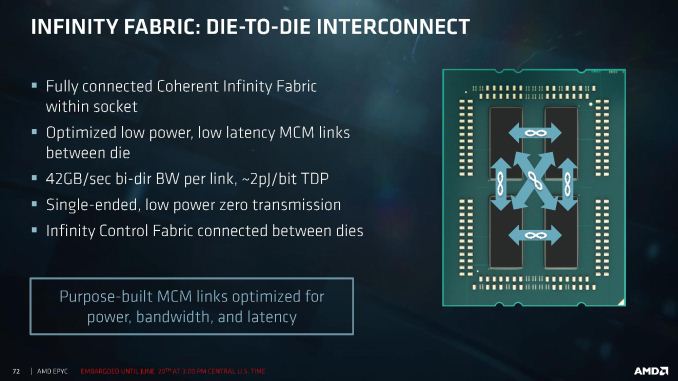

Judging from the diagram, I wonder if there will be any extra delay going from say top left to bottom right.

Maybe they should implement a cross at the center?

哦... 原來係咁

哦... 原來係咁

原帖由 Sandbo 於 2017-6-7 11:03 發表

$849 USD Thrradripper 16C/32T,

https://www.techpowerup.com/234114/amds-entry-level-16-core-32-thread-threadripper-to-reportedly-cost-usd-849

真係咁平,Intel今次連史都冇得食

原帖由 Puff 於 2017-6-12 03:04 發表

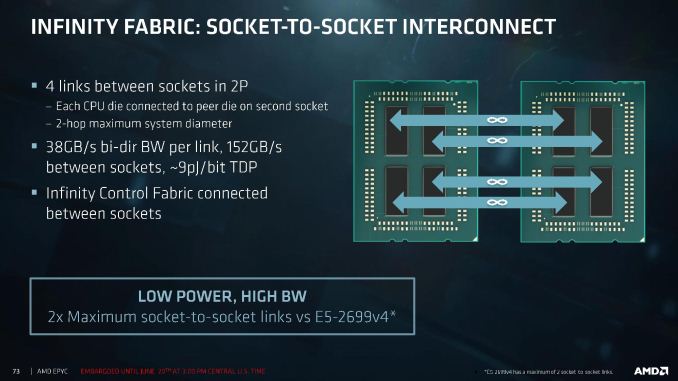

1/2S 32-core Naples 都喺夾埋出 x128

偷唔偷每粒都喺要兩條 x16 off-package

on-package 有幾多就唔知,但兩至三條拎走唔甩 (ring 4s/fully connected)

問題喺幾多 serdes lane 同 data rate ...

| 歡迎光臨 HKSpot (https://bbs.hk-spot.com/) | Powered by Discuz! 6.0 Lite |