引用:

原帖由 ccw 於 2011-7-5 20:10 發表

It looks around 15-20% improvement for the same frequency from SB.

原帖由 ccw 於 2011-7-6 01:21 發表

I am not sure, just a rumor from the web and a guess based on the bench.

原帖由 ccw 於 2011-7-6 01:32 發表

Somewhat I want to predict how much I will lose for buying a Sandy in Sep, and if it is worthwhile to further suspend the plan, through quite impossible.

原帖由 qcmadness 於 2011-7-6 01:40 發表

it depends on usage

if you need multi-thread performance, SB-E, BD, will be better than IVB

原帖由 ccw 於 2011-7-6 01:47 發表

Yes, but another question is I want to utilize ECC memory at the same time, I am not sure if SB-EP is still that avoidable to me.

And I am not sure about building an Opteron system, I cannot see a s ...

原帖由 ccw 於 2011-7-6 09:08 發表

It looks the upcoming bulldozer Opteron uses only Socket G34,

so it maybe hard to take BD as a choice.

原帖由 qcmadness 於 2011-7-6 09:19 發表

C32 also, but nearly the same infrastructure with Socket AM3+

And C32 is optimized for performance/power but not max performance

原帖由 ccw 於 2011-7-6 10:24 發表

Thanks for telling, I may take a look on the feasibility on building with those parts later.

原帖由 ccw 於 2011-7-6 10:38 發表

Not really a workstation, but a stable machine with satisfactory performance lasting for around 4 years within budget.

Therefore Xeon E3 should be a right choice for me, I simply thinking that if the ...

原帖由 ccw 於 2011-7-6 10:58 發表

You are correct with this,

I don't really need ECC but in case it is within budget, it is preferred.

I can accept the performance of SB Xeon and think that it would serve me well in a few years, so y ...

原帖由 ccw 於 2011-7-6 11:16 發表

That would no doubt be bringing a performance boost with 2C4T more, and also the quad channel memory will favor the editing in Photoshop, that is quite critical to me.

But the point is still on the b ...

2800

2800 原帖由 ccw 於 2011-9-15 09:40 發表

http://news.mydrivers.com/1/204/ ... om/1/204/204271.htm

2800

原帖由 qcmadness 於 2011-9-15 20:09 發表

發佈果陣一路都話係995M transistor (4-core version)

而家有人追問IVB transistor count

一口氣將SB個transistor count推上1140M

咁佢同BD個competitive advantage無左一大半 ...

原帖由 ccw 於 2011-9-15 20:35 發表

Maybe the advantage of Tri-Gate should be taken into account; the advancement may cover the loss due to the transistor number boost.

原帖由 qcmadness 於 2011-9-16 01:36 發表

http://www.anandtech.com/show/48 ... 5m-are-both-correct

愈講愈衰

As I mentioned above, Ivy Bridge finally supports USB 3.0 natively.

Quad-core Ivy Bridge CPUs will support up to 8MB of L3 cache, and the private L1/L2s haven't increased from their sizes in Sandy Bridge (32+32K/256K).

The memory controller also remains relatively unchanged, aside from some additional flexibility. Mobile IVB supports DDR3L in addition to DDR3, enabling 1.35V memory instead of the standard 1.5V DDR3. This is particularly useful in notebooks that have on-board DDR3 on the underside of the notebook; OEMs can use DDR3L and keep your lap a bit cooler.

Memory overclocking also gets a bump in Ivy Bridge. The max supported DDR3 frequency in SNB was 2133MHz, Ivy Bridge moves this up to 2800MHz. You can now also increase memory frequency in 200MHz increments.

The System Agent operates on a separate voltage plane than the rest of the chip. On Ivy Bridge Intel now offers even lower System Agent voltage options for the lower voltage SKUs, which in turn helps power optimize those SKUs.

The cTDP up mode is obviously for docked notebooks. You can imagine an Ivy Bridge notebook with an optional dock that could enhance the cooling capabilities of the machine. When undocked the notebook's processor would operate at a max TDP of 17W, for example, but toss it in a dock with additional cooling and the TDP would jump up to 33W. It's up to the OEMs to decide how they want to take advantage of this feature. It could be something as simple as a mobile dock with more fans, or something as complex as a modular water cooling solution with a bigger radiator in the dock. I haven't seen any concepts of systems that take advantage of Ivy Bridge's cTDP up support, but that's the theory.

What about cTDP down? Take the same 17W Ivy Bridge CPU from above but now drop the TDP to 13W, which in turn limits clock speed and voltage. Why would you want to do this? From the OEM perspective, Intel's TDP choices may seem arbitrary. Downwards configurable TDP allows OEMs to get a lower power configuration without forcing Intel to create a new SKU. OEMs can do this today through undervolting/underclocking of their own, but the cTDP down spec will at least give OEMs a guarantee of performance/power.

The Ivy Bridge GPU adds support for OpenCL 1.1, DirectX 11 and OpenGL 3.1. This will finally bring Intel's GPU feature set on par with AMD's. Ivy also adds three display outputs (up from two in Sandy Bridge). Finally, Ivy Bridge improves anisotropic filtering quality. As Intel Fellow Tom Piazza put it, "we now draw circles instead of flower petals" referring to image output from the famous AF tester.

Ivy Bridge will bring about higher clock speeds thanks to its 22nm process, however the gains will likely be minimal at best. Intel hasn't been too keen on pursuing clock speed for quite some time now. Clock for clock performance will go up by a small amount over Sandy Bridge (4 - 6%), combine that with slightly higher clock speeds and we may see CPU performance gains of around 10% at the same price point with Ivy Bridge. The bigger news will be around power consumption and graphics performance.

Ivy Bridge will be Intel's flagship 22nm CPU for some time. The chip was originally due out at the end of this year but was likely subject to delays due to issues with the fab process and the chip itself. The move to 22nm is significant leap. Not only are these new transistors aggressively small but the introduction of Intel's tri-gate technology is a major departure from previous designs. Should the fab engineers at Intel do their job well, Ivy Bridge could deliver much better power characteristics than Sandy Bridge. As we've already seen, introducing a 35W quad-core part could enable Apple (and other OEMs) to ship a quad-core IVB in a 13-inch system.

原帖由 ccw 於 2011-11-24 22:45 發表

http://news.mydrivers.com/1/210/210239.htm

原帖由 qcmadness 於 2011-9-18 09:49 發表

http://www.anandtech.com/show/48 ... hitecture-exposed/1

4 USB 3.0 ports across all high-end chipsets.

Still 2 SATA-3 and 4 SATA-2 ports.

A little bit disappoi ...

原帖由 qcmadness 於 2011-11-26 18:03 發表

架構... 好快intel要學amd / nvidia攪 heterogeneous multi-core

single-thread performance開始難升了

方向係咁, 但係點做到, 3間都有唔同的盤算

原帖由 Henry 於 2011-11-26 19:01 發表

如果Intel IB可以idle或部分Core開果陣可以關某幾個Core已經係省電上再進一步,四核Idle可以同單核睇齊,只用雙核既情況可以關雙核.

原帖由 Henry 於 2011-11-26 20:03 發表

所以可能要Windows出Patch Load曬所有Background落一粒槓桿CPU(Random)到,然後空出其他CPU比其他大食Program.

原帖由 Henry 於 2011-11-27 01:19 發表

K10/Barcelona......做壞左個頭,M$即刻縮沙.

但始終省得1W得1W係Notebook/Tablet既目標,Desktop某程度都要.

原帖由 qcmadness 於 2011-11-27 01:20 發表

M$係咁fing d thread usage

intel / amd都要設計到預左cpu係咁on / off / on / off

原帖由 qcmadness 於 2011-11-27 01:35 發表

http://www.xtremesystems.org/for ... ng-on-Windows-Seven

原帖由 Henry 於 2011-11-27 01:44 發表

叫HT某條Thread訓教.....

始終起動一個Core要相當時間,無可能又開又關,所以先會想到要將所有背景放係一個CPU到,其他可以關.

睇來到Win7 M$都係未做好優化,Core Parking泊錯車........

原帖由 Henry 於 2011-11-27 01:54 發表

HT由P4 3.06B開始已經開始有,D人都唔明點解HT原本Intel講到好勁但到Win就立即收皮.

但有D軟件真係開到HT個效能出來.....

但而家10年後,原本應該從特定軟 ...

(雖然我個人覺得同Win一樣)

(雖然我個人覺得同Win一樣) 原帖由 Henry 於 2011-11-27 02:13 發表

但Program使唔使要同OS講要幾多CPU,或等CPU自己分配?

同埋Linux果D背景係分散唔同CPU做定集中一個CPU管理?(雖然我個人覺得同Win一樣)

原帖由 Henry 於 2011-11-27 02:13 發表

但Program使唔使要同OS講要幾多CPU,或等CPU自己分配?

同埋Linux果D背景係分散唔同CPU做定集中一個CPU管理?(雖然我個人覺得同Win一樣)

原帖由 ccw 於 2011-11-28 10:34 發表

http://news.mydrivers.com/1/210/210479.htm

......再遲下可能S同K同頻.

......再遲下可能S同K同頻.

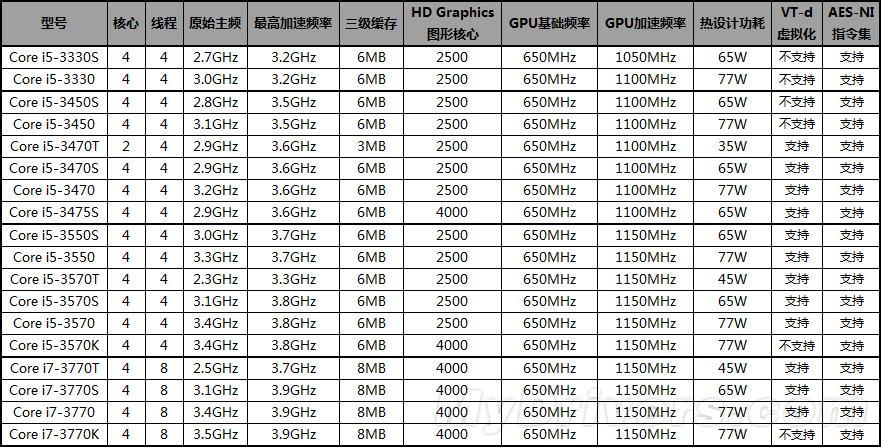

原帖由 Henry 於 2011-11-29 06:18 發表

但3770 Non-K終於用返最上級IGP,唔超既話都唔使為個IGP買K仔,而且又有VT-D.

i5要最上級IGP就一係S一係K.

| 歡迎光臨 HKSpot (https://bbs.hk-spot.com/) | Powered by Discuz! 6.0 Lite |