引用:

原帖由 qcmadness 於 2011-9-2 14:29 發表

http://www.intel.com/Assets/en_US/PDF/manual/248966.pdf

呢個係致命傷

16519

1個clock可以做既野

a. 2x 2 similar ADD/SUB

b. 2 similar ADD/SUB + 2 similar ADD/SUB/Logic Ops/LS Ops

c. 1 FP/SIM ...

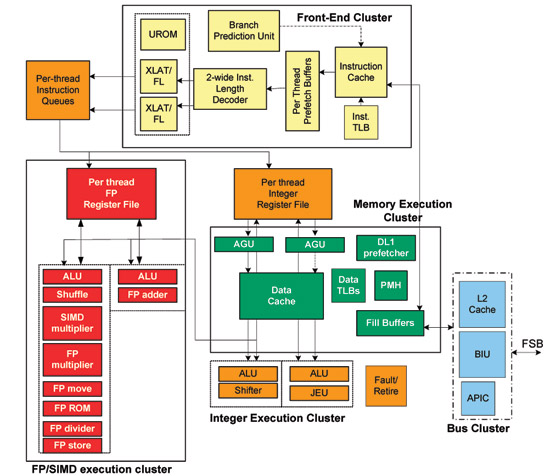

Port 0. In the first half of the cycle, port 0 can dispatch either one floating-point

move μop (a floating-point stack move, floating-point exchange or floating-point

store data) or one arithmetic logical unit (ALU) μop (arithmetic, logic, branch or store

data). In the second half of the cycle, it can dispatch one similar ALU μop.

Port 1. In the first half of the cycle, port 1 can dispatch either one floating-point

execution (all floating-point operations except moves, all SIMD operations) μop or

one normal-speed integer (multiply, shift and rotate) μop or one ALU (arithmetic)

μop. In the second half of the cycle, it can dispatch one similar ALU μop.

原帖由 qcmadness 於 2011-9-2 14:29 發表

http://www.intel.com/Assets/en_US/PDF/manual/248966.pdf

呢個係致命傷

16519

1個clock可以做既野

a. 2x 2 similar ADD/SUB

b. 2 similar ADD/SUB + 2 similar ADD/SUB/Logic Ops/LS Ops

c. 1 FP/SIM ...

原帖由 qcmadness 於 2011-9-2 15:58 發表

好明顯唔係...

major execution都係跟Core

http://www.realworldtech.com/pag ... 40208182719&p=6

你望到同Core幾乎一樣 ...

原帖由 qcmadness 於 2011-9-2 16:16 發表

no...

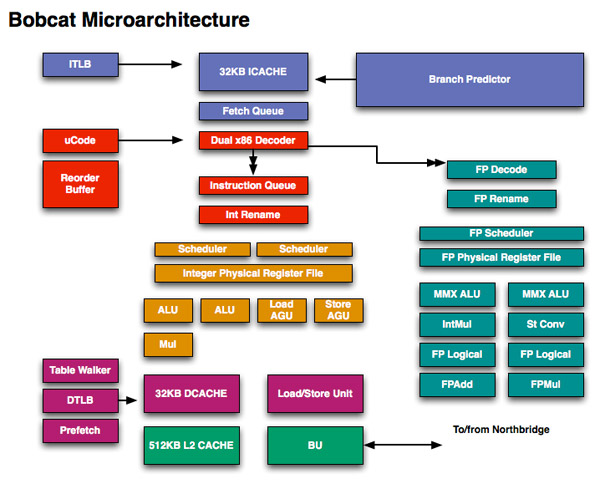

Bonnell同Bobcat都係只係每個issue到2個instruction

K10係3個

Core / Nehalem都係3 simple + 1 complex (complex可以拆開做2 simple)

原帖由 Henry 於 2011-9-2 16:26 發表

instruction呢到係uOps?

K10 => 3INT + 3FP,平行

Core/Nehalem => 3 INT/FP Mixed (唔知一個port可唔可以同時做兩樣野,應該唔得)

原帖由 qcmadness 於 2011-9-2 16:30 發表

唔係... 普通ADD / MUL之類的instructions

K7/K8/K10都係3組平行

但係其實有好多浪費, 連Bulldozer都唔再咁做

Core/Nehalem/SB都係4+1, 始終有d係Load/Store instruction

而K7/K8/K10/Bulldozer都係跟埋係integer ...

原帖由 Henry 於 2011-9-2 16:44 發表

見Nehalem同Core都係一個RS排曬隊,所有INT/FP都係曬一齊.

2/3/4原來係有,無Show......

Bulldozer個FP好似Intel咁排隊,而INT就3條各自排隊?

原帖由 qcmadness 於 2011-9-2 17:00 發表

no... 1個port只可以做1樣野

所以Core之後的Intel CPU, 有番咁上下memory performance

BD係unified FP scheduler, 1條隊

(Dual D2 667/800)

(Dual D2 667/800)

原帖由 Henry 於 2011-9-2 17:12 發表

配P/G965既年代,D RAM都仲係好慢.(Dual D2 667/800)

當然CPU Inter-core速度好快.

不過AMD應該同一時間能做多好多野,點解都係咁慢?

L1/L2/L3慢Fetch唔切? ...

原帖由 Henry 於 2011-9-2 17:20 發表

3ALU/FP + 3DATA,多一個/少一個都會失平衡,跟住就會慢.

不過Prediction係Netburst都唔死得既話,只有3+3應該唔會太大問題.

但係如果Intel既Prediction/cache speed + AMD BD既ALU/FP既排列..........:devlau ...

原帖由 Henry 於 2011-9-2 17:29 發表

ARM.....

個人覺得,Android咁樣無節制跑Multitasking既話,基本上無返粒i3咁上下都好難順.

當然而家Dual core ARM已經叫做好DD,但耗電實在令人擔憂.

Bonnell,睇來到係要製程.

除非有粒野再 ...

原帖由 qcmadness 於 2011-9-2 17:30 發表

Bonnell玩到in-order

Bobcat玩到half-speed L2

下次加埋core-gating同埋TurboBoost/Core

可能有得打

原帖由 Henry 於 2011-9-2 17:36 發表

core-gating?

TurboBoost/Core唔係長治久安之計,況且x86係效能方面應該唔使擔心.

只不過係idle果陣既對策就.....

而家私家車都玩start-stop,x86如果玩到idle唔開CPU(開timer)既話應該有得打. ...

原帖由 Henry 於 2011-9-2 17:41 發表

我指係索性關CPU/NB,只開CPU clock同receiver.

一有電話,即刻開CPU/開mon.

之前Intel好似開發到超低耗多核CPU,拎其中一個Core放落電話到,搞掂.

| 歡迎光臨 HKSpot (https://bbs.hk-spot.com/) | Powered by Discuz! 6.0 Lite |