引用:

原帖由 Puff 於 2014-1-30 17:23 發表

Ambiguous statement as usual. Not necessarily Cats I would say, but Cat's design methodology (automation driven) + higher per-core performance yet in a smaller size and nice perf/watt. If you look at ...

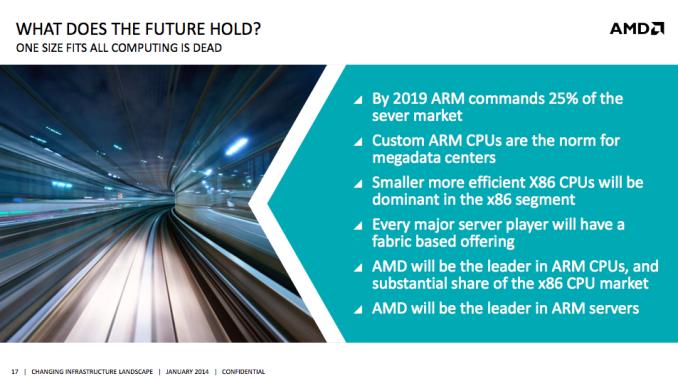

The real question is what architecture(s) AMD plans to use to get to a leadership position among ARM CPUs and a substantial share of the x86 CPU market. We get the first hint with the third bullet above: "smaller more efficient x86 CPUs will be dominant in the x86 segment".

原帖由 Puff 於 2014-1-30 17:23 發表

Ambiguous statement as usual. Not necessarily Cats I would say, but Cat's design methodology (automation driven) + higher per-core performance yet in a smaller size and nice perf/watt. If you look at ...

原帖由 Puff 於 2014-1-30 17:31 發表

thus the major diffs are the choice of heterogeneous solution and what are being used to address the bottom scaling over the spectrum. AMD may have a mid-term competitive advantage with ARM, as ARM i ...

原帖由 Puff 於 2014-1-30 17:36 發表

Whatever as it depends on whether Intel can break into that market with x86, or drastically turn the big ship towards ARM.

But the main idea is that AMD would likely converge their x86 lines ...

原帖由 Puff 於 2014-1-30 17:56 發表

I don't see contradiction. Basically I meant what you mean here.

Perhaps also with a lower frequency ceiling with regard to custom designs like Haswell or BD.

原帖由 Puff 於 2014-1-30 18:13 發表

The argument is that it is useless to build two cores, aiming for a similar power performance and scaling, but with different ISAs. It is clear that AMD targets just dense server, embedded and handhel ...

原帖由 Puff 於 2014-1-30 20:59 發表

I got one clear messages from AMDer and three signs from LinkedIn that may point to a custom ARM microarchitecture in the pipeline. Another clear message is Bulldozer's irreversible EOL.

原帖由 qcmadness 於 2014-1-30 21:05 發表

What kind of "custom" is taking place? CPU-CPU interconnect can be.

Bulldozer's EOL is known already.

原帖由 Puff 於 2014-1-30 21:10 發表

"High-level definition of core microarchitecture". There is another "ambidextrous" interconnect project supporting both x86/ARM SOC/chips. Probably ring based. probably.

Which means either ...

原帖由 qcmadness 於 2014-1-30 21:15 發表

Beefing up Jaguar is an option. It is already on par with K8 / Pilediver IPC wise.

原帖由 Puff 於 2014-1-30 21:18 發表

Literally means the same as convergence of two cores.

Anyhow, AMD already demonstrated their commitment to drive high-performance core towards Cat's automated design methodology in HC24.

原帖由 qcmadness 於 2014-1-30 21:19 發表

Not convergence

Improve from Jaguar using K10.5 and Bulldozer experiences

原帖由 Puff 於 2014-1-30 21:23 發表

You know what I mean. A far-stronger Jaguar capable of 3-3.5GHz clock would be nice. Give it more execution resources and larger windows, stick it with a ring interconnect and overhauled cache hierar ...

原帖由 Puff 於 2014-1-30 21:40 發表

Strong L/S system is preferred over more ALUs.

Say Load Queue with 64+ entries and Store Queue with 32+ entries.

Super fast L2 would be great, particularly

原帖由 Puff 於 2014-1-30 21:43 發表

I guess it would be fine for automated designs... ALU won't occupy too much space, but the L/S unit will. Server workloads rely on the perf of the later tho.

P.S. Broadcom Vulcan Core

原帖由 Puff 於 2014-1-30 21:50 發表

well I doubt it would be really a lot when you look at Intel's implementation. It just burns more transistors on decoding/microcode and a sophisticated load-store unit due to x86's strict memory orde ...

原帖由 qcmadness 於 2014-1-30 22:50 發表

Remember Intel has the highest-density cache in the industry.

And Intel has control over the fabrication / manufacturing.

原帖由 Puff 於 2014-1-30 23:11 發表

no matter how it goes, overprovision is always needed for diminishing IPC improvements. The 3.1mm2 Jaguar has a plenty of room to grow IMO, particularly when we are talking about perhaps FinFET based ...

原帖由 qcmadness 於 2014-1-30 23:30 發表

Even at 10mm^2, it is still small compared with Steamroller and Haswell

原帖由 Puff 於 2014-1-30 23:44 發表

plenty of options to fill that up

- less dense for higher frequency (single turbo up to 3+ Ghz would be nice)

- 3 ALU + 3 AGU as you suggested

- Pipelined Multiplier really helps... also better divis ...

原帖由 qcmadness 於 2014-1-30 23:46 發表

SMT is not that useful in client processors.

And I would expect AMD will re-focus in client processors rather than server processsors.

原帖由 Puff 於 2014-1-30 23:56 發表

I would say AMD always prioritizes servers over clients... But unfortunately their revenue is in a inverse way thanks to the epic Bulldozer. It is fairly easy to count what AMD would still stick to x ...

原帖由 qcmadness 於 2014-1-31 00:01 發表

In the past: true

Except the success of Bobcat and Jaguar, both of which are low-power client architectures.

| 歡迎光臨 HKSpot (https://bbs.hk-spot.com/) | Powered by Discuz! 6.0 Lite |