引用:

原帖由 qcmadness 於 2012-4-15 22:08 發表

咁而家都已經係 (Llano / SandyBridge), 點解仲要evolve?

你要明白要有效咁用埋GPU, OpenCL都睇得出唔會點流行, 唔merge佢地一齊用係大部分浪費

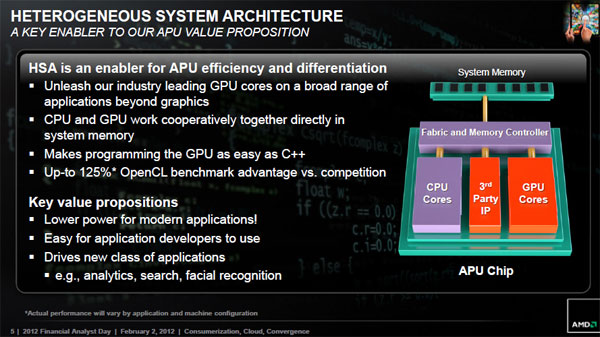

有效地運用 GPU 唔代表要 Merge 埋佢地一齊,OpenCL 流唔流行一件事,HSA 既出現就係為左你所講既野。

但係同 FPU replace with GPU 無乜關係喎。將 Speedy + Tightly Coupled to CPU pipeline 既 FPU 取代成 Slow + Loosely Coupled to CPU pipeline 既 GPU 係我最唔明白既事,呢兩個本來就係唔同既存在。完全唔同既 execution model.

HSA 既 purpose 就係 main path on CPU, tasks on either CPU and GPU.

You can still run branchy vector code on CPU with the FP unit, and run embarrassingly parallelizable code on GPU.